|

|

Разделы

Рекомендуем

|

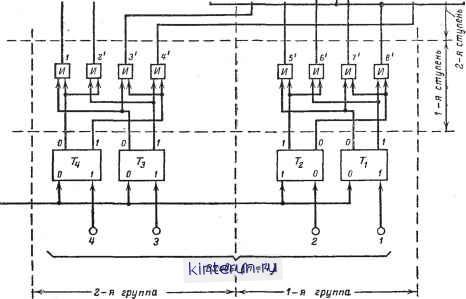

Автоматическая электрика Распространение радиоволн Выходы (к =16) /---------\ О 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Установка нуля  Рис. 11-162. функциональная схема двухступенчатого дешифратора на четыре входа. ОДНОЙ ИЗ НИХ (6 ) на оба входа поданы 1 [на другой вход этой схемы единица подается с ячейки И (2) первой ступени]. Триггер позволяет отпереть схемы И {9 -16 ) третьей ступени. Но единицы поданы на оба входа только одной схемы И {14 ). Поэтому единица возникает только на одном, 13-м выходе дешифратора. Аналогично при подаче на вход дешифратора любого другого числа в двоичной системе сигнал возникает на том его выходе, который соответствует данному числу. Число ступеней пирамидального дешифратора равно п-1. Первая ступень всегда имеет четыре двухвходовые схемы И и обслуживает два входа. Четыре выхода первой ступени подводятся на входы схем И второй ступени. Вторая ступень имеет всегда восемь двух-входовых схем И, они объединяют четыре выхода первой ступени с прямым и инвертированным третьим входом дешифратора (триггер Гз). Третья ступень имеет шестнадцать схем И, объединяющих восемь выходов второй ступени с прямым и инвертированным четвертым входом дешифратора, и т. д. С ростом пирамиды дешифратора количество схем в каждой новой ступе- ни увеличивается в 2 раза по сравнению с количеством схем в предыдущей ступени. Количество диодов, требуемое для построения пирамидального дешифратора, yV = 8(2 -> -1) . По сравнению с прямоугольным такой дешифратор имеет меньшее число диодов. Экономия особенно сильно проявляется при достаточно большом (п>4) числе входов. Многоступенчатые дешифраторы требуют еще меньшего количества днодов. Так, например, двухступенчатый дешифратор прн большом числе входов по числу днодов почти в *2 раза экономичнее пирамидального. При построении двухступенчатого дешифратора общее число входов разбивается на две одинаковые группы. (Если п нечетно, число входов одной из групп на единицу больше). Для каждой группы составляется одноступенчатый дешифратор. Все выходы одноступенчатого дешифратора одной группы объединяются в неповторяющихся комбинациях со всеми выходами другой группы через двухвходовые схемы И. Общее количество схем совпадений второй группы равно 2 . Общее количество диодов для построения двухступенчатого дешифратора: когда п четно, N = n2 -f 2-2 ; когда п нечетно, - -2 п-1 2 -f 2-2 . На рис. 11-162 приведена функциональная схема на четыре входа. При подаче на вход числа 1101 (13 в двоичной системе) высокие потенциалы (единицы) образуются иа правых выходах триггеров Гь Гз, Ti, в результате чего срабатывают схемы 4 и 6. Схема 4 подготавливает срабатывание схем с выходами 12- 15 (вторая ступень), а схема 6-схем с выходами /, 5, 9, 13. В результате выходной сигнал появится только на одном выходе 13, что соответствует числу 13, поданному на вход дешифратора. Наименьшее число диодов можно получить в схеме многоступенчатого дешифратора, построенного по определенному правилу. Число входов сначала разбивается на две группы, как в двухступенчатом дешифраторе. Каждая из полученных групп таким же образом разбивается на две подгруппы и т. д. Разбивку продол- , жают до тех пор, пока в каждой подгруппе не останется два или три входа. Образовавшиеся группы соединяют рядом двухступенчатых дешифраторов. Пример функцио- нальной схемы многоступенчатого дешифратора на девять входов приведен на рис 11-163. Входы подгрупп /-IV соединяются с дешифраторами первой ступени, имеющими 4 или 8 выходов в соответствии с числом входов в подгруппе. Число выходов каждого из дешифраторов первой ступени определяется как где т - число-входов в подгруппе. ) Выходы дешифратора первой ступени объединяются схемами И в полные группы неповторяющихся комбинаций (дешифратор h). Так, дешифраторы /i и 11\ дают 4 8=32 комбинации, так что дешифратор h имеет 32 выхода. Соответственно дешифраторы Uh и IVi дают 4-4=16 комбинаций, такое же количество выходов имеет дешифратор Ih. Наконец, дешифратор h имеет 32-16= =512 выходов. Для дешифратора, построенного по схеме на рис 11-163, требуется Л= (8-b24-f 8Н--f8)-f (32-2-H6-2)-f512-2=l 168 диодов, тогда как при построении двухступенчатого дешифратора на девять входов потребовалось бы 1 248 диодов, пирамидального - 2 040, а прямоугольного (одноступенчатого) - 4 608 диодов. Динамические триггеры Логические элементы с запоминанием могут быть как статическими, так и динамическими. В статических элементах запоминание осуществляется на длительное время, пока на вход не поступит новый сиг- Выходы(н=51г) Дешифратор иа 512 выходов Дешифратор на 32 выхода Дешифратор на Ч выхода. Дешифратор иа le Выходов i Г I i 1 - If Ч-----fEj----j---{-Mi - - -g- - Дешифратор иа 8 выходов Дешифратор на Ч выхода. Входы (п=9} I Дешифратор на Чвыхода Рис. 11-163. Функциональная схема многоступенчатого дешифратора на девять входов. нал, изменяющий это состояние (например, триггер, феррит-транзисторные ячейки и т. д.). Динамические элементы запоминают соответствующее состояние путем движения сигнала в схеме. Одним из необходимых условий работы динамических элементов является периодическая подача на .вход специальных периодических тактовых импульсов. Выход Вход 1

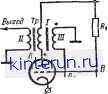

Вход О Рис. 11-164. Функциональная схема динамического триггера 0-К5Ов  + )5в -)5Ое0-С +гов Лее Л-К5в Вход 1 Вход О П+>5в -1г+ в -J-oe се Рис. 11-165. Схема лампового динамического триггера. Основным динамическим элементом, который часто используется в современных цифровых машинах, является динамический триггер. Он имеет два состояния 1 и 0. В отличие от статического триггера, где эти состояния различаются уровнем выходного напряжения, в динамическом триггере в состоянии 1 на выходе возникает периодическая последовательность импульсов, а в состоянии О - выходной сигнал отсутствует. На динамический триггер (рис. 11-164) поступает последовательность тактовых импульсов (от генератора импульсов ГИ) и управляющие сигналы 1 (вход /) или О (вход 0). При подаче на вход / импульса, совпадающего по времени с одним из тактовых импульсов, на выходе схемы И возникает импульс, который по цепи обратной связи, состоящей из устройства запоминания или задержки (например, линии ЛЗ) подается на вход схемы ИЛИ. Время задержки выбирается равным периоду следования тактовых импульсов. Поэтому им- пульс с выхода линии задержки, пройдя через схему ИЛИ, вновь поступает на схему И и совпадает со следующим тактовым импульсом. Следовательно, после перевода схемы в состояние 1 на выходе триггера возникает периодическая последовательность импульсов. При подаче импульса на вход О схема запирается, цепь обратной связи разрывается и выдача импульсов на выходе прекращается: триггер устанавливается в состояние 0. В качестве задерживающего или запоминающего элемента может использоваться не только линия задержки, но и конденсатор, колебательный контур или транзистор, в которых благодаря инерционным свойствам происходит как бы запоминание входного импульса. На рис. 11-165 приведен пример динамического триггера с одной лампой и диодными схемами И и ЗАПРЕТ. Запоминающим элементом является конденсатор С. В схеме выбрано здесь Rn.np-сопротивление диода в прямом направлении. В исходном состоянии напряжение на конденсаторе близко к нулю, диоды Дз и Дб, а также диод Д, отперты. Потенциалы точек А к В близки к нулю, лампа заперта (потенциал ее катода -М5 е) и тактовые импульсы не проходят на выход триггера. В результате подачи запускающего импульса на вход / конденсатор С быстро заряжается через диод Дв до напряже- ~С(-7В) ГЦ вб 0 0 JL-si Вход о Д, тг-м<-1 Вход! Тр -- Выход г JJ7 {имП11ЛЬ0Иый.) Выход I (потенциальный ) Рис. 11-166. Схема транзисторного динамического триггера. ния, близкого К амплитуде импульса. С прекращением импульса запуска начинается медленный процесс разряда конденсатора С через резистор R2, так что к моменту прихода очередного тактового импульса потенциал точки А сохраняется достаточно высоким, что позволяет этому импульсу пройти через схему совпадения Ди Дг, Ri на сетку лампы Л. В результате этого возникает импульс на выходе и по цепи обратной связи (обмотка III и диод Д5) произойдет подразряд конденсатора С, так

|

|

© 2010 KinteRun.ru автоматическая электрика

Копирование материалов разрешено при наличии активной ссылки. |