|

|

Разделы

Рекомендуем

|

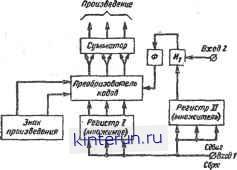

Автоматическая электрика Автоматика радиоустройств на выход схемы ИЛИ2. Этот импульс пос-, тупает на схему И6, открытую высоким потенциалом, с выхода Т триггера T-i-В результате действия импульса переноса сигналы переноса появляются на выходе схемы ИЛИ2 и ИЛИ4. Через время, равное времени задержки ЛЗ, эти сигналы изменяют состояния триггеров Ть-г и Уна противоположные. По окончании переходных процессов в сумматоре установится число 100, что соответствует сумме двух двоичных чисел: 011 и 001. Время выполнения операции сложения в рассмотренной схеме и-разрядного сумматора накапливающего типа со сквозным переносом определяется формулой Тсп = 2т + (и - 1)тп + Те, где т - время установления триггера; %п- время задержки в цепих переноаа одного разряда; т3 - время задержки в линии задержки. Если сумматор оперирует с числами, представленными в обратном коде, то время сложения определяется по формуле Теп = 2х + пхп +т8. Множительное устройство с сумматором параллельного действия. Рассмотрим множительное устройство, в котором умножение начинается со старшего разряда множителя. Частные произведения суммируются в сумматоре параллельного действия накапливающего типа. Процесс умножения двух чисел распадается на ряд элементарных операций, в число которых входят: - формирование знака произведения; - сдвиг множимого и множителя в регистрах; - анализ цифр множителя; - пересылка сдвинутого множимого в сумматор каждый раз, когда анализируемая цифра множителя - единица. Если анализируемая цифра множителя - нуль, пересылка в сумматор не производится. Для выполнения операции умножения необходимо иметь, кроме сумматора, еще два регистра, один из которых предназначен для хранения и сдвига множимого, а другой - для хранения и сдвига множителя. Формирование знака произведения выполняется путем сложения по модулю два знаковых разрядов множимого и множителя. Чаще всего эта операция реализуется на триггере знака регистра множимого. Полученный знак произведения в регистре множимого не сдвигается в процессе умножения, а управляет схемами передачи в сумматор сдвинутого множимого в прямом или обратном коде до конца выполнения операции умножения. На рис. 24-122 представлена упрощенная схема множительного устройства. Перед началом умножения в регистре I находится множимое, в регистре И- множитель. Сумматор установлен в нулевое положение. Процесс умножения начинается с подачи импульса сдвига на Вхъ при котором множимое в регистре I сдвигается вправо, а множитель в регистре II - влево на один разряд. После этого в старший разряд регистра II записывается, цифра стар-  Рис. 24-122. Множительное устройство с сумматором параллельного действия. шего разряда множителя. Содержимое данного разряда анализируется подачей импульса на Bxz. При этом на выходе схемы И] появляется импульс, если в старшем разряде множителя стоит 1, и не появляется, если в старшем разряде множителя стоит 0. Импульс на выходе И: после формирования поступает на преобразователь кодов, через который множимое заносится в сумматор в соответствующем коде и складывается с содержимым его. После этого на Вх\ снова подается импульс, сдвигающий множимое вправо, а множитель - влево на один разряд. После сдвига на Вх2 подается импульс, управляющий пересылкой сдвинутого множимого в сумматор. Этот процесс повторяется столько раз, сколько разрядов содержит множитель. По окончании умножения в сумматоре будет записано произведение в прямом коде, если знак произведения положительный, и в обратном (или дополнительном), если знак произведения отрицательный. Для выполнения операции умножения n-разрядных двоичных чисел без округления необходимо иметь в сумматоре и регистре множимого 2п разрядов, что приводит к большому объему оборудования. Можно упростить арифметическое устройство, если операцию умножения выполнять с округлением. Для получения ошибки округления не больше заданной число разрядов в сумматоре и регистре множимого увеличивают на гсд. Тогда сумматор и регистр имеют по п+ +пд разрядов. Выбор числа дополнительных разрядов пд можно осуществить из условия, чтобы максимальная ошибка от округления при выполнении операции умно- жения не превосходила заданной величины. Максимальная абсолютная ошибка округления Да0Кмакс в рассматриваемом сумматоре возникает при умножении двух п-разрядных чисел: 0,111.....1 и 0,111...11 Схема умножения для этого случая представлена на рис. 24-123. Множимое f*-/! Рнс. 24-123. К схеме умножения, изображенной на рис. 24-122. Максимальную абсолютную ошибку умножения в единицах младшего 2п-го разряда можно определить из выражения ,= \-2х> + 2-21 + +3-22 -j-----Ь mSt гДе m = n-пд. Если принять выполнение неравенства I ДСок макс 2п, то можно определить количество дополнительных разрядов из соотношения (п - пд - 1) 2*~ Д + 1 < 2И+1. (24-96) В общем случае время умножения для рассматриваемой схемы можно определить по формуле Гумн = (Гол + TCR)n. (24-97) Однако если сдвиг осуществляется в регистре множимого во время выполнения операции сложения, то Уумн = 7слп, (24-98) где 7 сл- время сложения чисел в сумматоре; п-количество двоичных разрядов множителя. Из формул (24-97) и (24-98) следует, что время выполнения операции умножения в п раз больше, чем время сложения двух чисел. Как показал анализ задач, решаемых на цифровых машинах, количество операций умножения составляет около 40% от всех остальных операций. Отсюда ясно, что для увеличения общего быстродействия необходимо стремиться к уменьшению времени выполнения умножения. Существуют различные методы сокращения времени выполнения умножения. Один из них состоит в том, что создаются комбинационные множительные устройства из логических быстродействующих элементов! Время выполнения операции умножения в таком устройстве определяется в основном переходными процессами в логических схемах. Количество оборудования в таком множительном устройстве резко растет с увеличением числа разрядов. Другим методом сокращения времени умножения является одновременное умножение на несколько разрядов множителя, что можно осуществить в множительных устройствах как с последовательным, так и с параллельным сумматором. При осуществлении одновременного умножения на несколько разрядов множителя требуется незначительное увеличение оборудования. В настоящее время разработаны схемы одновременного умножения на два и три разряда. Кроме рассмотренных методов, сокращение времени умножения можно осуществить за счет пропусков нулей Множителя. При умножении на нуль время на пересылку множимого не отводится, а отводится лишь на выполнение сдвига. Таким образом, при умножении на. нуль время тратится лишь на сдвиг, а при умножении на единицу - на сдвиг и сложение. Сокращение времени умножения можно получить, применяя схемы для запоминания переносов с последующим суммированием их с частным произведением. Этот метод требует для реализации увеличения оборудования и усложнения логической схемы арифметического устройства. В тех случаях, когда применяется сумматор с последовательным переносом, целесообразно ввести групповые переносы, с целью уменьшения времени. При этом частота посылки множимого в сумматор выбирается не из максимального времени переноса по всем разрядам, а из максимального времени переноса на число разрядов в группе. В конце каждой группы имеется элемент для запоминания единиц переноса. Этот метод требует небольшого увеличения оборудования арифметического устройства и позволяет значительно сократить время выполнения операции умножения. Деление в арифметическом устройстве параллельного действия. Схема арифметического устройства для выполнения операции деления зависит от того, какой способ деления двоичных чисел выбран. Рассмотрим схему, выполняющую деление в прямом коде в машине с фиксированной запятой по способу без восстановления остатка. Для реализации деления по этому способу необходимо выполнить ряд элементарных операций: формирование знака частного; определение возможности деления; определение разрядов частного; определение конца деления. Формирование знака частного производится путем сложения на одноразрядном сумматоре знаковых разрядов делимого и делителя. Определение возможности деления выполняется путем вычитания модуля делителя из модуля делимого. Положительный1 знак остатка означает, что делимое больше цессов в сумматоре на Вхг подается сигнал. На выходе схемы И2 появляется сигнал, если знак остатка положительный, и не появляется, если знак остатка отрицательный. При положительном знаке остатка (Ганг в нулевом положении) в младший разряд регистра II записывается единица - старший разряд частного. ЗходЭ 0- Вход г Вход/ На стоп Сумматор Гкодов. Регистр 1 гт~т Вход -0 1 t t Регистр В Вход ч -0 Рис. 24-124. Схема арифметического устройства для выполнения операции деления. делителя и деление невозможно вследствие переполнения разрядной сетки сумматора. Отрицательный знак остатка означает, что делитель, больше делимого, т. е. деление возможно. Для определения разрядов частного необходимо осуществлять сдвиг делителя вправо, вычитание или прибавление его к остатку, анализ знака остатка и запись единицы нли нуля в младший разряд регистра частного. На рис. 24-124 представлена упрощенная схема арифметического устройства, выполняющего, операцию деления по способу без восстановления остатка. Исходное состояние схемы: в сумматоре находится делимое в прямом коде, в регистре I - делитель, также в прямом коде. Триггер знака Г3щ регистра I установлен в единичное положение. Деление начинается с подачи сигнала на Вх, в результате чего производится вычитание делителя из делимого. По окончании переходных процессов в сумматоре подается сигнал опроса на Вх\. Если знак остатка в сумматоре положительный, то на выходе схемы Hi появляется сигнал, указывающий на невозможность деления ввиду переполнения разрядной сетки. Если знак остатка отрицательный, то деление возможно. Определение цифр частного начинается с подачи сигнала опроса на Вхз. Этот сигнал устанавливает триггер ТзяЬ в состояние, противоположное состоянию триггера знака остатка ТЗН2. После этого на Вхц подается сигнал, сдвигающий делитель на один разряд вправо. По окончании переходных процессов, связанных со сдвигом, на Вх снова подается сигнал переписи, который переписывает сдвинутый делитель в сумматор. После окончания переходных про- Для определения второго разряда част-1 ного на Вхз подается сигнал, устанавливающий триггер знака T3Hi регистра I в состояние, противоположное состоянию триггера знака остатка. Далее сдвигается делитель в регистре I вправо и частное в регистре II влево на один разряд подачей сигнала на Вх4, после чего последовательно подаются сигналы на Вх, Вх%, Вхз и т. д. Рассмотренный процесс повторяется до получения частного с количеством разрядов, определяемым разрядной сеткой машины. Процесс деления заканчивается или специальным счетчиком, или путем занесения единицы в младший разряд регистра II перед началом деления. При этом переход триггера старшего разряда регистра II из единичного состояния в нулевое будет означать конец деления. По окончании деления частное будет записано в регистре II в прямом коде. 24-10. УСТРОЙСТВО УПРАВЛЕНИЯ Устройство управления (УУ) цифровой машины служит для обеспечения автоматической работы машины по заданной программе, а также для управления машиной с пульта. Устройство управления в процессе работы вычислительной машины должно обеспечить прежде всего автоматический ввод программы с внешнего запоминающего устройства в оперативное, выборку команд нз оперативного запоминающего устройства на регистр команд для исполнения, а также выборку чисел из оперативного запоминающего устройства по адресу, указанному в адресной части команды., и передачу их в регистр арифметического устройства.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2010 KinteRun.ru автоматическая электрика

Копирование материалов разрешено при наличии активной ссылки. |