|

|

Разделы

Рекомендуем

|

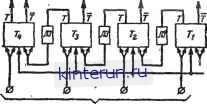

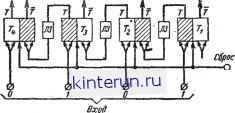

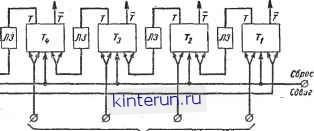

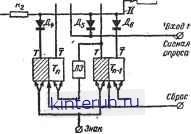

Автоматическая электрика Автоматика радиоустройств числу разрядов слагаемых. Параллельные сумматоры могут быть как комбинационными, так и накапливающими. На рис. 24-116 представлена функциональная схема параллельного сумматора комбинационного типа. На схеме обозначено: Xi, t)i- входы для цифр первого и второго слагаемых; Pi-переносы из младших разрядов в старшие; 2,- - одноразрядные сумматоры на три входа каждый. Я. ft -5ft. *> Si ft . t Pi Pi LTTU e, Сумма Рис. 24-116. Функциональная схема параллельного сумматора комбинационного типа.  CSpee Шаг) BxaS Рис. 24-117. Схема параллельного сумматора накапливающего типа. На входы каждого одноразрядного сумматора одновременно подаются цифры Xi и tji соответствующих разрядов слагаемых и цифра переноса из младшего разряда. Сумма на выходе возникает сразу по окончании переходных процессов. . Единицы, переноса, возникающие в младших разрядах, передаются в старшие. В предельном случае единица переноса может пройти от младшего разряда к самому, старшему. В приведенной схеме время, необходимое для выполнения операции сложения, складывается из времени переходного процесса в одноразрядном сумматоре. Наиболее распространенными являются сумматоры параллельного действия накапливающего типа. В этих сумматорах в качестве основного элемента используется одноразрядный сумматор на триггере. В сумматоре накапливающего типа подача слагаемых разделена во времени. На рис. 24-117 дана схема параллельного сумматора накапливающего типа. В этом устройстве в качестве одноразрядного сумматора применена триггерная схема, рас- смотренная ранее. В общем случае сумматор состоит из п триггерных ячеек 24, Т2, Тп (в нашем случае из четырех), цепей установки сумматора в нулевое положение и сдвига, цепей ввода слагаемых и передачи единицы переноса из младших разрядов в-старшие. В цепях переносов включены линии задержки с временем, несколько большим, чем время переходного процесса в триггере при изменении его состояния. Рассмотрим основные режимы работы сумматора. а) Суммирование двух двоичных чисел. Перед занесением первого слагаемого все триггеры устанавливаются в нулевое положение импульсом, подаваемым на шину  (сдвиг) Рис 24-118. К рис. 24-117. Сброс. На вход сумматора подается первое слагаемое. При занесении единицы в какой-либо разряд соответствующий триггер изменяет свое состояние на обратное. При занесении нуля состояние триггера не изменяется. Пусть в сумматоре установлено первое слагаемое, равное х=0101. На рис. 24-118 показан сумматор, в котором записано число х=0101. Штриховкой обозначены закрытые половины триггеров, на выходах которых имеется высокий потенциал. Подадим на вход сумматора второе .слагаемое #=0110. При подаче второго слагаемого состояние триггеров Тг, Т4 не меняется. Подача импульса, соответствующего единице, на вход триггера Т2 изменяет его состояние на обратное. Триггер Т% переходит из нулевого состояния в единичное, что вызывает положительный перепад напряжения на выходе Т этого триггера, который через задержку поступит на счетный вход триггера Т3. Импульс, поданный на вход триггера Т3, устанавливает его в нулевое состояние, благодаря чему на выходе триггера Тъ возникает отрицательный перепад напряжения, который через задержку поступит на счетный вход триггера 7V Благодаря наличию в цепях связи линий задержек ЛЗ положительные и отрицательные перепады напряжения на входы триггеров Т3 и Т4 поступают через время т3 по окончании переходного процесса в каждом триггере. Эти перепады на входах триггеров дифференцируются. После дифферен- Знак  Мантисса Рис. 24-119. Сумматор чисел, представленных в обратном модифицированном коде. цирования на вход триггера Т3 будет действовать импульс положительной полярности. Этот импульс не изменяет состояния триггера Т3. После дифференцирования отрицательного перепада напряжения на вхо- + 0- Упр. сигнал  (сдвиг) Рис. 24-120. Схема представления знака числа. де триггера Tt возникает отрицательный импульс (единица переноса из младшего разряда в старший). Этот импульс через диоды поступает на вход триггера и устанавливает его в единичное положение. В результате операции сложения триггеры будут установлены в положение, соответствующее числу 1011, т. е. сумме двух чисел: х + у = 0101 +0110= 1011. Для изображения знаков чисел и суммы отводятся дополнительные триггеры. На рис. 24-119 изображена схема сумматора, работающего с числами, представленными в обратном модифицированном коде. В этом сумматоре триггеры Тв, Те - знаковые. Цепь, соединяющая выход Т триггера Те с входом триггера Ти называется цепью циклического переноса. Если сумматор работает с числами, представленными в дополнительном модифицированном коде, то цепь циклического переноса разрывается. Представление знака в сумматоре дву- мя- разрядами вызвано удобством определения переполнения разрядной сетки. На рис. 24-120 представлены два знаковых триггера, в выходных цепях которых включены две логические схемы И, каждая на три входа. Выходы схем И объединены посредством логической схемы ИЛИ. Сигнал на выходе схемы ИЛИ появляется всякий раз, когда состояние триггеров соответствует комбинации 01 или 10, и не появля- ется, если состояние триггеров соответствует комбинации 00 или 11. Сопротивление R\ и диоды Дь Д2, Дз составляют одну схему И на три входа. Сопротивление R2 и диоды Д4, дб, Де составляют вторую схему И на три входа. Кратко остановимся на работе этой схемы.. - После выполнения операции сложения на Вх\ подается положительный импульс для анализа состояния триггеров. Этот импульс опроса закрывает диоды Д2 и Д5. На шине / или шине II возникает импульс положительной полярности, если-диоды Дь Д3 или Д4, Де закрыты высокими уровнями напряжения, снимаемыми с выходов знаковых триггеров. Диоды Дь Дз будут закрыты лишь в том случае, если триггер Т находится в нулевом состоянии, а триггер Tn-i - в единичном. Диоды Д4, Д6 будут закрыты, если триггер Тп находится в единичном состоянии, а триггер Tn-i- в нулевом. Следовательно, на шине / возникает импульс положительной полярности при подаче на Bxi сигнала опроса при состояниях триггеров Тп, Тп-и соответствующих 01. На шине возникает импульс положительной полярности при состояниях триггеров Тп, Тп-ь соответствующих 10. Сигнал с выхода схемы ИЛИ при возникновении переполнения может быть использован для дальнейшего управления машиной. б) Установка сумматора в нулевое состояние (сброс сумматора). Установка сумматора в нулевое сотояние осуществляется подачей на шину Сброс отрицательного импульса длительностью, удовлетворяющей неравенству Ти > Тз, где ти- длительность импульса сброса; тэ - время задержки в линии задержки. Отрицательный импульс, поданный на шину сброса, устанавливает триггеры в нулевое положение. Импульсы переноса, возникшие при этом, не изменяют состояния триггеров старших разрядов вследствие того, что они поступают до прекращения действия импульса сброса. в) Выполнение операции сдвига. Сдвиг числа, стоящего в сумматоре, осуществляется подачей на шину Сброс (Сдвиг) отрицательного импульса, длительность которого должна удовлетворять неравенству Ти < Тз. Импульс сдвига подобно импульсу сброса изменяет состояние лишь тех триггеров, которые находятся в единичном положении. При переходе триггеров из единичного состояния б нулевое появляются сигналы переноса, которые через время т3 поступают на входы триггеров старших разрядов после прекращения действия импульса сдвига и изменяют их состояния на обратные. Направление сдвига определяется способом включения линий задержки. В сумматоре, схема которого показана на рис. 24-119, сдвиг числа осуществляется влево на один разряд при действии каждого импульса сдвига. Рассмотренный сумматор является параллельным сумматором накапливающего типа с каскадным (последовательным) переносом. Вследствие применения каскадного переноса максимальное время, необходимое для выполнения операции сложения в сумматоре с циклическим переносом, опреде- ляется временем переходных процессов триггеров т и временем задержки т3 сигналов переноса. Максимальное время выполнения операции сложения в n-разрядном сумматоре определяется формулой Тел ~ (п+ 1)Т -г-ИТз. Для сокращения времени выполнения операции сложения можно заменить последовательный перенос из одного разряда в другой сквозным переносом. В разряд сумматора, в который поступил сигнал переноса, записывается единица, а все разряды, через которые прошел перенос, устанавливаются в нулевое положение. На рис. 24-121 представлена схема трех разрядов параллельного сумматора накапливающего типа со сквозным переносом. Основным элементом данного сумматора является одноразрядная суммирующая схема, представленная на рис. 24-109. Рассмотрим работу трех разрядов сумматора со сквозным переносом при сложении двух двоичных чисел, начиная с момента, когда первое слагаемое 011 находится в сумматоре (триггеры Tfe, Тъ-t, Tk-г) > второе слагаемое 001 - в регистре (триггеры Tk, Tt .it Tft 2)- Для выполнения операции сложения подается импульс на Вх2, который переносит содержимое регистра в сумматор. По окончании переходных процессов в цепих связи и триггерах в сумматоре будет установлено число 010, после чего подается импульс переноса на Вх3, который проходит через открытую схему И2 п г Установка нуля -QBxoBt -0ВхоВЗ ИЛИ. ИЛИ, г J ЛИ, Импульс переноса -0&а>вг Импульс сложения Рис. 24-121. Схема трех разрядов сумматора накапливающего типа со сквозным переносом.

|

|

© 2010 KinteRun.ru автоматическая электрика

Копирование материалов разрешено при наличии активной ссылки. |