|

|

Разделы

Рекомендуем

|

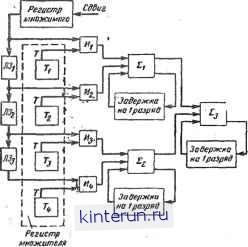

Автоматическая электрика Автоматика радиоустройств Перед сложением в регистре х находится первое слагаемое х=х% х2... хп, в регистре у находится второе слагаемое у- ~Уи Уг -.. у-п. Триггер Т± установлен в состояние, соответствующее нулю. При этом схемы И] и И2 закрыты. Подачей сигнала Вход 0- слога ей ого х Вхевг 0- Регистр х Сдвиг Вход 0- слагаекого у Вход/ 0-Н Г, Задержка на /разряд Рнс. 24-112. Суммирующее устройство последовательного действия со статическими регистрами. Регистр X Устройство регенерации Выход/ *-1 Вхав/ -Н- Вход/ Вхевг Регистр У Устройство регенерации Задержка на 1 разряд Рис. 24-113. Суммирующее устройство последовательного действия с динамическими регистрами. на Bxi триггер Т, устанавливается в состояние, соответствующее 1; схемы Hi и И2 высоким потенциалом с выхода Т открываются для передачи слагаемых на вход сумматора 2. После окончания переходного процесса в триггере Tt на Вх2 поступают импульсы сдвига, каждый из которых сдвигает слагаемые -вправо на один разряд. Импульсы сдвига продвигают на сумматор слагаемые разряд за разрядом, начиная с младших. Результат суммирования младших разрядов с выхода сумматора поступает на вход регистра х и занимает освободившийся разряд. Возникшая единица переноса при сложении разрядов слагаемых поступает через элемент задержки на вход сумматора одновременно с очередными разрядами слагаемых. Описанный процесс повторяется столько раз, сколько разрядов содержат слагаемые. По окончании операции сложения в регистре х находится сумма, а регистр у установлен в нулевое положение. Сумма из регистра х может быть использована для дальнейших вычислений или записана в запоминающее устройство. На рис. 24-113 представлена функциональная схема последовательного суммирующего устройства, в регистрах которого слагаемые хранятся в динамическом режиме. Устройство регенерации служит для восстановления и формирования цифр слагаемых после прохождения через регистр. В качестве регистров в данной схеме могут служить различные элементы задержки. В регистры х и у через устройства регенерации вводятся слагаемые. Перед вводом слагаемых триггер Ti устанавливается в единичное состояние, при котором схема И1 открыта, а схемы И2, И3 закрыты. Слагаемые х и у непрерывно циркулируют в своих регистрах. При подаче на Вх2 импульса, разрешающего сложение, триггер Ту устанавливается в нулевое положение, при к<> тором высоким потенциалом с выхода Т схемы И2, И3 открываются. Вместе с этим низким потенциалом с выхода Т схема Hi закрывается. Слагаемые через открытые схемы И2, И3, начиная с младших разрядов, поступают в сумматор. Полученная сумма поразрядно поступает в регистр х через устройство регенерации. В момент прихода старшего разряда суммы подается импульс на Bxt, устанавливающий триггер Ti в единичное состояние, при котором закрываются схемы И2, И3 и открывается схема Hi. На этом заканчивается выполнение операции сложения двух чисел. По окончании выполнения операции сложения в регистре х циркулирует сумма, а в регистре у - по-прежнему второе слагаемое. Динамические регистры для надежной работы на больших частотах (> I Мгц) требуют применения специальных мер по стабилизапии величины задержки. Скорость подачи цифр слагаемых из статических сдвигающих регистров определяется частотой подачи сдвигающих импульсов, а скорость подачи цифр слагаемых из динамических регистров определяется временным интервалом между импульсами, представляющими цифры слагаемых. Время сложения двух -разрядных чисел в суммирующих устройствах последовательного действия можно определить приближенно по формуле Тслитс, (24-94) где тс -: временной интервал между разрядами (временной интервал между сдвигами). Сложение отрицательных чисел в суммирующих устройствах последовательного действия наиболее целесообразно производить в дополнительном коде. Это вызвано тем, что при выполнении операции сложения в дополнительном коде отсутствует циклический перенос, осуществление которого в суммирующих устройствах последовательного действия требует дополнительного оборудования и увеличивает время выполнения операции сложения. При дальнейшем рассмотрении арифметических устройств последовательного действия будем также предполагать наличие на входе и выходе сумматора преобразователей кода, позволя- Регистр частных сумм и произведения Вход ВыХСд Вход/ Входг Регистр множимого на/розрод Задержка Регистр множителя УР д\ \l Вход о Bxodl чВыход Рис. 24-114. Множительное устройство последовательного действия. ющих преобразовывать отрицательные числа в дополнительный код, а дополнительный код - в прямой. Последовательное множительное устройство. Как извест-hov выполнение операции умножения двоичных чисел распадается на операции суммирования и сдвига. Знак произведения формируется путем сложения по модулю два знаковых разрядов сомножителей. При последовательной работе сдвиг числа в сторону старших разрядов производится задержкой его в регистре на количество временных интервалов, соответствующее числу разрядов, на которое желательно осуществить сдвиг. Последовательное устройство для умножения чисел в двоичной системе счисления может быть построено на основе описанного выше последовательного суммирующего устройства (рис. 24-113). На рис. 24-114 представлен один из вариантов последовательного устройства для умножения. Устройство содержит три регистра: для множимого, множителя и регистра частных сумм, где по окончании умножения хранится произведение. Устройство выполняет ряд сложений сдвинутого множимого с содержимым ре- гистра частных сумм. Сложение управляется цифрами множителя, начиная с младшего разряда. Перед началом умножения множимое и множитель в прямом коде циркулируют в фазе , т. е. цифры одноименных разрядов появляются на выходе регистров одновременно, регистр частных сумм и произведения находится в нулевом состоянии, триггеры Tt и Т2 установлены в такое положение, при котором схемы И2, Не, И7 закрыты, схемы Иь И4 открыты. В момент, когда цифры младших разрядов множимого и множителя выходят из регистров, на Вх2 подается сигнал, устанавливающий триггер Т\ в состояние, при котором схемы И2, И3, Ив открыты, схемы Иь И4 закрыты. На вход схемы И5 от генератора импульсов ГИ подается сигнал. Если цифра множителя - единица, то сигнал ГИ через открытую схему И5 устанавливает триггер Т2 в состояние, при котором схема И7 открывается. Множимое через открытые схемы Ив, И7 и сумматор поступает в регистр частных сумм и произведения, после чего подается сигнал на Вх\ триггера Ti, устанавливающий его в исходное состояние, при котором закрываются схемы И2, И3, И6 и открываются схемы Иь И4. Триггер Т2 подачей сигнала на Вхо устанавливается снова в исходное состояние, при котором схема И7 закрывается. Если цифра множителя - нуль, то триггер Т2 остается в исходном состоянии и схема И7 закрыта. Обозначим период повторения импульсов (временной интервал между разрядами) через тс и предположим, что умножение n-разрядных чисел происходит без округления, тогда второй разряд множителя должен появиться на выходе своего регистра через время г, равное f = (2га + 1)Тс. (24-95) Время t определяет период повторения им пульсов ГИ. При выборе периода повторения импульсов ГИ по формуле (24-95J цифры множителя будут появляться на входе схемы И5 одновременно с импульсами ГИ. Если вторая цифра множителя равна единице, то импульс от ГИ пройдет через открытую схеуу И5 и изменит состояние триггера Т2, который откроет схему И7. При этом множимое поступит на сумматор и сложится с содержимым, находящимся в регистре частных сумм и произведения. Однако на этот раз множимое будет задержано на один разряд (на время тс), что соответствует сдвигу влево на один разряд мно жимого перед сложением с предшествующим частным произведением. Задержка множимого осуществляется элементом задержки на один разряд, включенным в цепь регенерации множимого. Описанный процесс повторяется п раз. Множимое сдвигается (задерживается) на одни разряд в каждом такте. Сдвинутое множимое прибавляется к содержимому регистра частных сумм и произведения, если цифра множителя - единица, и не прибавляется, но сдвигается, если цифра множителя - нуль. Если регистры обладают емкостью 2 п разрядов каждый, то время, потребное на умножение двух п-разрядных чисел, можно приближенно определить по формуле Туыя = 2и2тс. Время умножения является произведением периода циркуляции 2птс на число разрядов множителя п. Основным достоинством устройств последовательного действия является сравнительная простота и небольшое количество оборудования. Существенный выигрыш в оборудовании можно получить, если вместо триггер-ных регистров использовать линии задержки различной конструкции, регистры на магнитных сердечниках или иметь запоминающее устройство с последовательной выборкой чисел. Время выполнения операции умножения может быть существенно уменьшено, если одновременно суммировать пары частных произведений в отдельных одноразрядных сумматорах. На рис. 24-115 представлена одна из возможных схем устройства для умножения четырехразрядных двоичных чисел. Перед умножением множимое и множитель вводятся в свои регистры. Каждая из линий задержек JT3i, Л32, Л33 задерживает множимое на один разряд. В результате этого на схемы Иь И2, И3, И4 поступает множимое, сдвинутое в сторону старших разрядов на 0, 1, 2, 3 разряда соответственно. Схемы Иь И2, И3, И4 управляются триггерами регистра множителя. На выходе схем Иь И2, Из, И4 появляются частные произведения, которые суммируются попарно на соответствующих одноразрядных сумматорах. С выходов сумматоров 2i и 22 парные произведения поступают на последний одноразрядный сумматор 23, на выходе которого возникает произведение двух чисел. Рассмотренное множительное устройство образовано двумя группами одноразрядных сумматоров. Количество групп (ступеней) одноразрядных сумматоров зависит от количества разрядов множителя и может быть определено из неравенства 2s>n>T~\ где п-количество разрядов множителя; s - число групп (ступеней) одноразрядных сумматоров. Количество одноразрядных сумматоров должно быть на единицу меньше числа двоичных разрядов множителя. Если принять задержку каждого сумматора на время, равное интервалу между разрядами тс, а временных интервалов при умножении двух n-разрядных чисел 2п-1, то время умножения без округления может быть выражено формулой Тумв = (2п - 1)Тс + SXs ИЛИ При Tt=Tc Ууын = (2п- 1 + S)Xc. Произведете  Рис. 24-115. Устройство для умножения четырехразрядных двоичных чисел. Рассмотренное устройство позволяет значительно уменьшить время умножения, но требует для своей реализации большого количества оборудования. Построение множительного устройства по приведенной структуре может быть целесообразным при наличии простых одноразрядных сумматоров. Существенным недостатком арифметических устройств последовательного действия следует считать их малое быстродействие. Для увеличения быстродействия целесообразно применять в последовательных арифметических устройствах динамические элементы, устойчиво работающие на больших частотах. Арифметическое устройство параллельного действия Параллельное суммирующее устройство. В отличие от сумматора последовательного действия, в котором цифры слагаемых вводятся последовательно, начиная с младших разрядов, а процесс сложения развертывается во времени, в параллельном сумматоре сложение во всех разрядах чисел производится одновременно. Сумматор параллельного действия состоит из одноразрядных суммирующих схем, количество которых соответствует

|

|||||||||||||||||||||||

|

© 2010 KinteRun.ru автоматическая электрика

Копирование материалов разрешено при наличии активной ссылки. |