|

|

Разделы

Рекомендуем

|

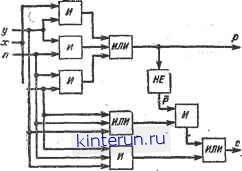

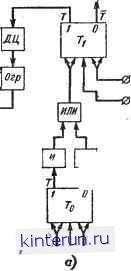

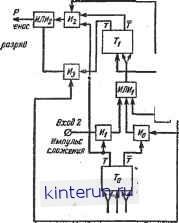

Автоматическая электрика Автоматика радиоустройств сигналы, соответствующие единицам. В этом случае на выходе схемы одноразрядного сумматора будет иметь место сигнал суммы с=1 и сигнал переноса р=\. I Уравнение для суммы можно значительно упростить, если сумму с выразить с помощью инверсии р, для чего выберем из табл. 24-8 сочетания, при которых р=0, тогда р=плхлу\/плхлу\/п/\х/\у\/ упЛхлу- (24-92) Умножив логически обе части уравнения (24-92) на (х Уум п), получим: рА(хуууп)= =(пЛхлу\/пл,хлу\/плхлу\/п/\хлу)л А(хуу\/п)=пг\ хлхлу\/п/\хлхлу\/ \/пЛхлхлу\/пЛ.хлхлу\плхлу/\у V Vti/\x/\yлуУплх/\уЛу\/ п/\х/\у Л лу\/плплхлу\/плпл хлу\/п/\ ЛплхлуУплплхАу- Учитывая, что хАх=уА У = п ап=0 и ХАх=х, уАУ=у, пАп=п, будем иметь: р А (XV yV п)=ПА X А у v я л ХА yV П А ~ХА у~. Полученное выражение можно подставить в правую часть уравнения суммы (24-91), тогда С=рА(х\/у\/п)\/пАХАу, (24-93) p=XAy\jn,AyytlAX. ) На рис. 24-107 представлена схема сумматора, построенная по уравнениям (24-93). Возможны и другие варианты логических схем сумматоров. Выбор варианта схемы сумматора зависит от того, какие логические элементы используются при его построении. Входные сигналы при работе с комбинационным сумматором могут быть либо импульсного, либо потенциального ти па. Тип сигнала зависит от выбранных логических элементов. Одноразрядный сумматор накапливающего типа. Одноразрядный сумматор накапливающего типа представляет собой счетчик по модулю г, где г - основание системы счисления, в которой представляются числа в машине. Накапливающий сумматор может иметь или два входа для каждого слагаемого отдельно, или один вход. Как в том, так и в другом случае слагаемые подаются на вход сумматора последовательно во времени и значение суммы будет определяться как результат сложения всех слагаемых, введенных в разное время. В качестве сумматора, предназначенного для сложения одноразрядных двоичных чисел, может служить триггер со счетным входом. На рис. 24-108, а представлена одна из возможных схем одноразрядного сумматора накапливающего типа и показаны временные диаграммы работы его (рис. 24-108,6) без. учета переноса из младшего разряда. Сумматор состоит из триггера Т± со счетным входом, дифференцирующей цепочки ДЦ и ограничителя Огр.  Рис. 24-107. Схема одноразрядного сумматора, построенного по уравнению (24-93). Триггер Т0 относится к одноименному разряду регистра. Связь между триггером сумматора Т± и триггером регистра Т0 осуществляется через логические элементы И;, И0, ИЛИ. Дифференцирующая цепочка ДЦ и ограничитель Огр служат для формирования импульса переноса в следующий разряд. Перед занесением первого слагаемогб триггер Т± импульсом, подаваемьгм на Вх\ устанавливается в нулевое положение, после чего подачей импульса на Вх2 производится перепись содержимого триггера Г0 в триггер сумматора Tt. Если в триггере Тй была установлена единица, то схема W\ будет открыта и импульс, поданный на Вх2, через схемы Hi и ИЛИ поступит на счетный вход триггера Т\. Триггер Т[ установится в состояние, соответствующее единице. При переходе триггера Т\ из состояния 0 в состояние 1 на выходе Т триггера Тг появляется положительный перепад напряжения. После его дифференцирования возникает положительный импульс, который через ограничитель не проходит, вследствие чего переноса в старший разряд в этом случае не будет. Если в триггере Т0 был записан 0, то подача сигнала на Вх2 не изменит состояния триггера 7\. Рассмотрим работу сумматора, когда триггеры Т0 и Т± установлены в состояние, соответствующее единице. Импульс, поданный на Вх2, проходит через схемы Иь ИЛИ на счетный вход триггера 7[ и изменяет его состояние на обратное. Триггер Tt при этом переходит из состояния 1 в состояние 0. На выходе Т триггера Ti возникает отрицательный перепад напряжения, после дифферен-  Перенос из младшего разряда Вход/ / I Перенос в старший v разряд Вход 3 0-Н И, и0 +-0 Вход О Выход 7 7> Выход .Выход Огр Рис. 24-108. Одноразрядный сумматор накапливающего типа и временные диаграммы его работы. цирования которого отрицательный импульс проходит через ограничитель в старший разряд. Информация с выхода Г триггера Т0 снимается в обратном коде через схему Ио при подаче импульса на Вхо. Работа остальных элементов схемы аналогична рассмотренному. В одноразрядном сумматоре, представленном на рис. 24-108, импульс переноса формируется путем дифференцирования перепада напряжения на единичном выходе триггера сумматора. При построении суммирующих схем на статических триггерах возможно формирование импульса переноса другим способом, основанным на использовании логических элементов. На рис. 24-109 представлена одна из схем одноразрядного сумматора, в которой сигнал переноса формируется при анализе состояний триггеров Ti и Г0. Рассмотрим работу схемы. Пусть в триггерах Т\, Т0 записаны единицы, а из младшего разряда на Вх4 поступает сигнал переноса, соответствующий единице. Для выполнения сложения на Вх2 подается импульс, который переносит содержимое Г0 в триггер Ti в прямом коде. Для переписи содержимого регистра на сумматор в обратном коде служит цепь, проходящая через И0. Импульс сложения в этом случае должен быть подан на Вх0. В результате действия импульса, поданного на Вхг, триггер Ti изменяет свое состояние с единицы на нуль. По окончании переходных процессов на выходе Т триггера Ti установится низкий потенциал, а на выходе Т-высокий. При этом схема Иг открыта высокими потенциалами с выходов Г триггера Ti и Т триггера Т0. Для передачи переноса в следующий разряд подается сигнал на Вх3, который проходит в цепь переноса через открытую схему И2 и схему ИЛИг. Сигнал переноса из младшего разряда поступает на вход схемы Из. Так как схема В стерший  Импульс переноса КйВхоВЗ &Bxadt Перенос т младшего разряда ЛЗ\-г-0Вхе0 * QSxodO Рис. 24-109. Одноразрядный сумматор накапливающего типа, в котором импульс переноса формируется при анализе состояний триггеров сумматора и регистра. И3 закрыта низким потенциалом свыхода Т триггера Ti, то сигнал переноса через И3 на вход схемы ИЛИ2 не проходит. Однако через линию задержки ЛЗ и схему ИЛИа этот же сигнал поступает на вход триггера Tt и изменяет его состояние на единичное. Та- ким образом, в результате сложения трех единиц в триггере сумматора будет записана единица и сформирован импульс пере носа в старший разряд. Рассмотрим работу сумматора, когда в триггере Го установлена единица, в триггере Ti - нуль, а из младшего разряда поступает сигнал переноса. ботов т l Г, Во/ход f I -Р-1-3= Вы в Т I Выходу В од к а3 [ Выход ход Z Вход 3 Вход *, Вход t Рис. 24-110. Временные диаграммы работы сумматора, изображенного на рис. 24-109. Для выполнения сложения на Вх2 подается импульс, после действия которого триггер Ti будет установлен в единичное состояние. По окончании переходных процессов на Вх3 подается импульс переноса. Этот импульс не проходит в цепь переноса через схему И2, закрытуюнизким потенциалом с выхода Т триггера 7. Импульс переноса из младшего разряда проходит на выход схемы ИЛИг через схему Из, открытую высоким потенциалом с выхода Т триггера Ti. Этот же импульс, задержанный линией задержки ЛЗ, изменяет состояние триггера 7V Триггер Ti устанавливается в положение, соответствующее нулю. Таким обра ом, при сложении двух единиц в сумматоре будет записан нуль и сформирован сигнал переноса в старший разряд. > На рис. 24-110 представлены временные диаграммы, иллюстрирующие работу сумматора. Оба рассмотренных одноразрядных сумматора накапливающего типа находят применение на практике. Первый сумматор имеет простую схему формирования переноса, второй - требует большего количества оборудования, но сложение в этом случае четко разделено на два такта. В первом такте выполняется сложение по модулю два, во втором -- формирование переноса. Такое временное разделение создает некоторые удобства при согласовании работы арифметического устройства с устройством равления. Арифметические устройства последовательного действия Последовательное суммирующее устройство. До сих пор рассматривались одноразрядные сумматоры с тремя входами, позволяющие выполнять сложение трех одноразрядных чисел.

Перенос Сумма Рис. 24-111. Сумматор последовательного действия. На основе одноразрядных сумматоров создаются сумматоры для сложения -разрядных чисел. В сумматорах последователь-, ного действия операция суммирования п-разрядных чисел выполняется поочередно разряд за разрядом, начиная с младшего. Последовательный сумматор может состоять из одной одноразрядной суммирующей схемы на три входа и устройства задержки единицы переноса. На рис. 24-111 представлена блок-схема сумматора последовательного действия. На вход сумматора подаются одноименные разряды слагаемых и разряд переноса. Сигнал переноса подается на вход сумматора через линию задержки одновременно с цифрами следующего старшего разряда. Таким образом, последовательная работа выполняется с цифрами, поступающими в порядке возрастания номеров разрядов. В качестве элемента задержки для единиц переноса применяются линии задержки различного конструктивного выполнения. Могут использоваться также различные запоминающие элементы. На рис. 24-112 приведена схема последовательного суммирующего устройства с использованием двух статических сдвигающих регистров для хранения слагаемых. Опишем кратко работу схемы.

|

|

© 2010 KinteRun.ru автоматическая электрика

Копирование материалов разрешено при наличии активной ссылки. |