|

|

Разделы

Рекомендуем

|

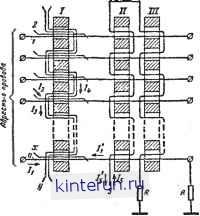

Автоматическая электрика Автоматика радиоустройств идентичность характеристик отверстии в платах оказывается меньшей, чем у партии сердечников, которые могут1 быть тщательно отбракованы. Отсюда вытекает целесообразность применения системы .типа Z для построения запоминающего устройства на ферроплатах. минания. Количество плат в переключателе равно количеству разрядов запоминаемых чисел, т. е. каждая плата переключателя обслуживает одну пару запоминающих плат. Платы переключателя собираются в пакет, который можно рассматривать как одну плату соответствующей толщины. Z56 отВерстий Ребра. Плато платы 6u& спереди Рис. 24-103. Ферритовая плата. а - общий вид; б - схема элемента платы. В запоминающем устройстве типа Z, собранном на ферритовых платах, через каждое отверстие проходят только два провода. Один провод, выполненный методом металлизации поверхности платы, последовательно проходит через все отверстия данной платы и служит для считывания и записи информации. Второй провод пронизывает отверстия, расположенные в пакете плат. Число таких проводов равно числу адресов запоминающего устройства. Эти провода называются адресными. Для увеличения надежности записи и считывания, уменьшения помех, возникающих вследствие непрямоугольное петли гистерезиса ферроматериала, на каждый разряд запоминаемого числа используется два отверстия двух плат. Таким образом, для запоминания -разрядных чисел требуется 2п ферроплат. Управление записью и считыванием по заданному адресу может осуществляться, например, магнитным переключателем, собранным из таких же плат, что и для запо-23-1248  Рис. 24-104. Схема прошивки магнитного переключателя и запоминающих плат. На рис. 24-104 представлена схема прошивки проводами одней пары запоминающих плат II, III и платы магнитного переключателя I. Прошивка плат производится так, что на одной плате адресный / и считывающий (перезаписывающий) 5 провода расположены согласно, а на другой плате эти провода расположены встречно. Каждая ячейка памяти расположена вдоль адресного провода. Пакет плат магнитного переключателя / прошивается координатными проводами 2 по рядам х и 3 по столбцам у, а также проводом смещения 4, который последовательно проходит через все отверстия магнитного переключателя. Для обращения по заданному адресу в соответствующие координатные провода х и у подаются импульсы тока /2 .и /3 (рис. 24-104). В отверстиях возбужденного ряда и столбца магнитное поле поданных импульсов тока компенсирует магнитное поле смещения, а в месте пересечения возбужденных проводов результирующее магнитное поле оказывается достаточным для перемагничивания феррита вокруг отверстия магнитного переключателя. При изменении магнитного состояния феррита вокруг отверстия платы магнцтного переключателя в адресном проводе / наводится э. д. с, под действием которой происходит считывание хранящегося по данному адресу числа. После считывания числа информация пропадает. При записи чисел на соответствующие координатные провода по- даются импульсы тока /2, /3, как и при считывании. После снятия импульсов тока /2, /3 с координатных проводов магнитный материал вокруг отверстий, расположенных на пересечении этих проводов, под действием тока смещения h возвращается в исходное состояние. При этом в адресном проводе, возникает импульс тока /?, полярность которого противоположна считывающему импульсу тока /. В момент действия импульса тока /2 на считывающий провод 5 подается импульс записи /5 или /5, полярность которого определяется записываемой цифрой. Пусть выбранным координатным проводом будет провод а на рис. 24-104. Условимся, что для записи единицы подается импульс, создающий ток /5, для записи нуля-импульс, создающий ток h Тогда в отверстии платы / будут складываться магнитные поля, создаваемые токами /5 и / j. Суммарного магнитного поля достаточно для перемагничивання феррита вокруг отверстия платы /, тогда как магнитные поля, создаваемые токами /5 и /j в отверстии платы , вычитаются и суммарное магнитное поле недостаточно для перемагничивання материала вокруг данного отверстия. После записи единицы вокруг выбранного отверстия платы III магнитный материал изменит магнитное состояние, а вокруг отверстия платы магнитное состояние не изменится. Для записи нуля в провод 5 подается импульс тока /5, по: лярность которого противоположна полярности импульса Is. При этом изменение магнитного состояния материала происходит вокруг отверстия платы II.- В этом случае при считывании информации единицы и нули будут отличаться полярностью сигнала, что увеличивает надежность работы устройства. Для восстановления считанной информации служит цепь регенерации, которая управляется считанными сигналами и сигналами записи. Основными достоинствами запоминающего устройства на феррнтовых платах являются: высокая технологичность, позволяющая автоматизировать процесс производства; сравнительно низкая стоимость; малые габариты и вес при большой емкости запоминающего устройства; возможность получения сравнительно малого времени обращения (до 3 мксек). 24-9. АРИФМЕТИЧЕСКИЕ УСТРОЙСТВА Арифметическое устройство (АУ) цифровой машины служит для выполнения арифметических и логических операций и является одной из наиболее важных частей цифровой машины. От выбора схема АУ, ею элементов, а также выполняемых операций зависят основные параметры машины: быстродействие, надежность, вес, габариты и т. д. Все арифметические операции (сложение, вычитание умножение, деление) могут быть сведены к операциям сдвига, арифметического сложения и преобразования ко-, дов. В соответствии с этим основными частями АУ являются сумматор, выполняю щий сложение двух чисел, сдвигатель и преобразователи кодов: Сумматоры Сумматор может быть построен из элементарных схем, каждая из которых служит для сложения только трех цифр: две из иих являются цифрами одноименных раз- х у п Р С Рис. 24-105. Функциональная схема полного одноразрядного сумматора. рядов слагаемых, третья - цифрой переноса из соседнего младшего разряда. Такую схему часто называют полным одноразрядным сумматором или сумматором на три входа. Результат на выходе полного сумматора является двухразрядным числом, состоящим из цифры переноса в старший разряд и цифры, представляющей собой сумму в данном разряде. Три цифры, поступающие на вход сумматора, могут быть сложены за два последовательных такта сложения, если в каждом такте складываются лишь две цифры. Сумматор, предназначенный для сложения лишь двух цифр, частоназывают сумматором на два входа или полусумматором. На выходе полусум--матора возникает сумма и перенос для каждой парывходных цифр. Схематическое изображение полного одноразрядного сумматора дано на рис. 24-105, где х - цифра некоторого разряда первого слагаемого; у - цифра того же разряда второго слагаемого;, п - перенос из предыдущего младшего разряда; р - перенос в последующий старший разряд; с - сумма. Одноразрядный сумматор комбинационного типа. Одноразрядный сумматор комбинационного типа имеет три входа, на которые одновременно подаются цифры одноименных разрядов двух слагаемых и цифра переноса из младшего разряда. При подаче слагаемых на вход комбинационного сумматора на выходе его сразу после окончания переходных процессов появляются сумма данного разряда и перенос в старший разряд. Сумма и перенос возникают в нем как результат комбинаций входных величин. Рассмотрим принцип построения одноразрядного сумматора комбинационного типа на три входа. В зависимости от значений цифр слагаемых в данном разряде и наличия или отсутствия единицы переноса из младшего разряда получаются различные значения суммы и переноса в старший разряд. В табл. 24-8 представлены значения суммы с и переноса р в старший разряд в зависимости от комбинации слагаемых х, у и переноса п из младшего разряда. Таблица 24-8 Составим логические уравнения одноразрядного сумматора. Уравнения составляются для значений суммы, с и переноса р, для чего выписываются все комбинации по строкам, которые дают единицу для суммы и переноса отдельно. Тогда * с-п/\хАуУпАХАуУпАхАуУ \/плхлу- (24-88) В этом уравнении первый член пах а у описывает комбинацию трех слагаемых для второй строки табл. 24-8, второй член паха у- для третьей строки таблицы, третий член пах А у - для пятой строки и последний член пАхау - для восьмой строки таблицы. Аналогично составляется логическое уравнение для переноса в старший разряд: р=пАхАуУПАХАУУПАХАуУ VnAxAy.- (24-89) Следовательно, логические уравнения, описывающие работу полного сумматора, имеют вид: С=ПАХАУ\/ПАХА уУПАХАуУ Упахау; р=ПАХАуУПАХАуУПАХАуУ УПАХАу- (24-90) Одноразрядный сумматор, построенный по уравнениям (24-90), должен иметь восемь схем И на три входа и две схемы ИЛИ на четыре входа. 23* Уравнения (24-90) можно преобразовать к более простой форме. Преобразуем уравнение, описывающее перенос, для чего логически прибавим к правой части уравнения для р (24-90) два члена пАхАу. Тогда получим: Р=ПАХАУУПАХАУУПАХАУУ УПАХАуУПАхАуУПАХАУ= =хАуА(пуп)упАуА(хУх)У УПАХА(УУУ)=ХАУУПАУУПАХ. Уравнения, описывающие работу комбинационного одноразрядного сумматора, примут вид: С=ПАХАУУПАХАУУПАХА АуупАХАу; р=ХАуУПАуУпАх. (24-91) Подстановкой легко убедиться, что (уравнения (24-91) удовлетворяют требованиям сложения трех цифр. На рис. 24-106 приведена схема одноразрядного сумматора, построенная на логических элементах по уравнениям (24-91). На выходе схемы возникают сумма и перенос для любой из восьми возможных комбинаций входных величин, указанных в табл. 24-8. ими., ft х ~Т и3-*и/>и Рис. 24-106. Схема одноразрядного сумматора, построенная по уравнению (24-91). Например, если все три входных сигнала п, х, у соответствуют единицам (восьмая строчка табл. 24-8), то на выходе схем И4- Ие сигналы будут отсутствовать, а на выходах схем И7-Ию появятся сигналы, соответствующие единицам. .При этом на выходах схем ИЛИц, ИЛИ12 также появятся

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

© 2010 KinteRun.ru автоматическая электрика

Копирование материалов разрешено при наличии активной ссылки. |