|

|

Разделы

Рекомендуем

|

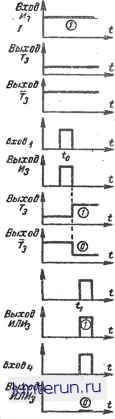

Автоматическая электрика Автоматика радиоустройств Импульс записи  Импульс Считывания Вход Импульс считывании Вход, Выход ® xodi Выход Выход Тг Выход: ИМИ, l Lb. ti ® Выход г Вход, Выход 4

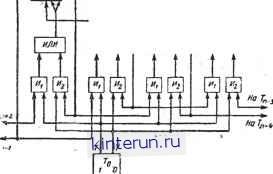

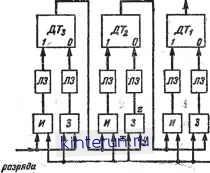

Выход ИЛИ, Bb/XOdi  Рис. 24-69. Временные диаграммы работы регистра. ных процессов в регистре будет записано число 101. Из регистра число может быть передано на выход в прямом или же обратном коде. Считывание записанного числа в прямом коде производится подачей импульса в момент времени tt на Bxs. Для считывания числа в обратном коде подается импульс на Bxi. Схемы логического сложения ИЛИ1, ИЛИг, ИЛИз служат для передачи прямого или же обратного кода числа на выходные шины. На рис. 24-69 показаны временные диаграммы, поясняющие работу регистра в режимах записи и считывания двоичных чисел. Сдвигающие регистры. Сдвигающий регистр служит для запоминания числа и сдвига его на один или несколько разрядов вправо или влево. На рис. 24-70 изображена простейшая схема сдвигающего регистра, позволяющего осуществлять сдвиг влево. В приведенном сдвигающем регистре выход одного триггера соединен с входом следующего, но не непосредственно, а через линии задержки ЛЗ. Для рассмотрения работы регистра предположим, что в нем записано число 011. Для сдвига числа, стоящего в регистре, на вход Установка в 0 подается отрицательный импульс, длитель- 71Д jjl гнД  Рис. 24-70. Сдвигающий регистр со сдвигом влево. ность которого меньше, чем время задержки. Этот импульс устанавливает все триггеры в положение, соответствующее. 0. При переходе триггеров из состояния 1 в состояние 0 на выходах Т триггеров 7Л, Т2 появляются отрицательные перепады напря- жения, которые после задержки и дифференцирования поступают на триггеры Т2 и Т3, устанавливая их в положение, соответствующее 1. По окончании переходных процессов в регистре будет установлено число 110, т. е. исходное число 011, сдвинутое иа один разряд влево. При подаче второго импульса сдвига в регистре установится число 100 и т. д. Выход Выход Выход хтл. И*пульс записи Импульсы сдвига U LJ U U Рис. 24-71. Временные диаграммы работы сдвигающего регистра со сдвигом влево. На рис. 24-71 даны временные диаграммы, поясняющие работу регистра со сдвигом влево. Для выполнения операции сдвига вправо необходимо соединить через линии задержки выход старшего разряда с входом младшего так, как это показано на рис. 24-72.  триггера То в положение, соответствующее 0, схемы И2 открываются высоким потенциалом с выхода Т триггера То, а схемы Hi закрываются, низким потенциалом с выхода 7 триггера То. В этом случае при подаче импульса сдвига на Bxj записанная информация сдвигается влево. В регистрах со сдвигом на статических триггерах каждый триггер срабатывает при сдвиге два раза. Один раз срабатывает при действии импульса сдвига и второй раз при передаче на его вход сигнала от линии задержки. Время сдвига Тед можно определить из формулы Тед = 2т + т3] (24-86) где т - время переходного процесса триггера; т3-время задержки импульса в ЛЗ. Сдвигающие регистры могут быть выполнены на- динамических триггерах. На рис. 24-74 представлен регистр со сдвигом вправо иа динамических триггерах. Регистр имеет общий вход для импульсов сдвига. Каждый динамический триггер имеет два входа для установки триггера в состояния, соответствующие 1 и 0. На входах каждого динамического триггеравключены логические схемы И и 3. Схема запрета реализует логическую функцию вида г=х < у. На вход 1 триггера EJi сигнал сдвига проходит через схему И и устанавливает его в состояние 1 лишь в том случае, если динамический триггер старшего разряда находится в положении, соответствующем 1. Если триггер старшего разряда находится в положении 0, то импульс сдвига проходит через схему запрета на другой вход триггера и устанавливает его в положение, Й т Н Т > Н Т -г В 7 -1 Установка SO и сдвиг --0 Рис. 24-72. Сдвигающий регистр со сдвигом вправо. Наконец, на рис. 24-73 дан один из вариантов схемы регистра со сдвигом вправо и влево. Схемы И служат для переключения выходов триггеров регистра. Управление схемами И осуществляется с помощью г* триггера То- При подаче импульса на Вх2 триггера То последний устанавливается в по-ложение, соответствующее 1, при котором схемы Hi открыты высоким потенциалом с выхода Т триггера То, а схемы И2 закрыты низким потенциалом с выхода Т триггера То. Импульс, поданный на Вхи будет сдвигать число в регистре вправо. При установке OxodZ Вход3 Сброс  Рис. 24-73. Реверсивный сдвигающий регистр. соответствующее 0. Каждый сдвигающий импульс производит сдвиг содержимого регистра на один разряд вправо.  Отставшего 0 Импульс сйвиеа Рнс. 24-74. Сдвигающий регистр на динамических триггерах. В данной схеме динамический триггер срабатывает при подаче каждого сдвигающего импульса лишь один раз. Время сдвига можно определить по формуле ! Тд.т + Тз, (24-87) где Тд.т- время переходнего процесса динамического триггера; т3-время задержки импульса сдви-1 га во входной цепи триггера. Дешифраторы Устройства, позволяющие выделять из серии импульсов отдельные импульсы или же распределять сигналы по шинам н заданном порядке в зависимости от комбинации сигналов на входе, называются дешифраторами или избирательными схемами. На рис. 24-75 представлена схема дешифратора, распределяющая сигналы по выходным шинам в зависимости от состояния триггеров двухразрядного счетчика. Сопротивление Ко и диоды До составляют логическую схему И. Сигнал на шине 0 появится лишь в том случае, если катоды диодов До, подключенных к нулевым выходам (Т) триггеров Тг, Tt, будут находиться под высоким потенциалом. В противном случае напряжение Е поГасится на сопротивлении Ко. Сопротивления Ко, Ri, Rz, Кз выбираются много большими прямых сопротивлений диодов. Сопротивление Ri и диоды Mi образуют также логическую схему И, сигнал на выходе которой появляется при состоянии триггеров 01. Следовательно, сигнал на выходе шины 1 появится лишь тогда, когда триггер 7Л будет находиться в единичном состоянии, а триггер Т2 - в нулевом. На шине 2 появится сигнал при состоянии триггеров 10, а на шине 3 - при состоянии триггеров 11. Количество диодов, потребное для построения подобного одноступенчатого дешифратора, может быть определено по формуле Q = п-2и, где, и - число триггеров в счетчике или регистре. При увеличении числа триггеров в счетчике или регистре, работающих совместно с дешифратором, потребное количество диодов резко увеличивается. Для сокращения потребного количества диодов применяются многоступенчатые де-шифраторы. Идея построения многоступенчатых дешифраторов состоит в том, что используются общие элементы в цепях формирования выходных сигналов. На рис. 24-76 изображена схема регистра с двухступенчатым дешифратором на 16 выходов. Первая ступень образована одноступенчатыми дешифраторами I и II. Вторая ступень образована диодной сеткой III. Для уяснения работы данного двухступенчатого дешифратора рассмотрим, например, при каком состоянии триггеров Тх - Т4 на шине 10 будет сигнал в виде высокого потенциала. На шине 10 сигнал появится лишь в том случае, если все диоды, подключенные к шине, будут закрыты. к, А -ОВхсЙв Установка в О Рис. 24-7S. Схема дешифратора. К шине 10 подключены диоды Д5 и Д4, к катодам которых подключены диоды До, Mi и Д2, Дз- Диоды Ms, Mt будут закрыты, если будут закрыты диоды Мо - Дз- Эти диоды закрываются лишь при состоянии триггеров регистра, соответствующем, двоичному числу 1001, т. е. триггеры Tt, Ту должны находиться в единичном состоянии, а триггеры Т3, Тг - в нулевом. Легко убедиться в том, что при любом другом состоянии триггеров регистра на шине 10 будет низкий потенциал. Общее число диодов в двухступенчатом дешифраторе можно определить по формулам: при п четном; Q2 = 2 +Ц.22

|

|||||||||||||||||||||||||||||

|

© 2010 KinteRun.ru автоматическая электрика

Копирование материалов разрешено при наличии активной ссылки. |